FPGA中的细粒度和粗粒度

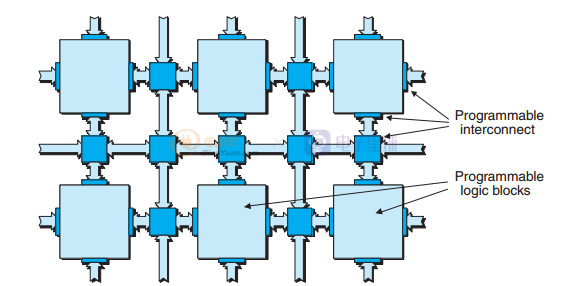

通常将FPGA产品划分为细粒度或粗粒度。这两个词是什么意思呢?首先,我们需要提醒自己,FPGA与其他器件的主要区别是,它们的底层结构主要由大量相对简单的“可编程逻辑块”组成,这些块镶嵌在可编程互连的结构中。

在细粒度的架构下,每个逻辑块只能实现一个非常简单的功能。例如实现一个三输入函数逻辑块。

而在粗粒度的架构下,相比于细粒度架构,每个逻辑块都包含大量的逻辑。例如,一个逻辑块可能包含四个4输入的LUTs、四个多路复用器、四个d型触发器和一些快速进位逻辑。

关于架构粒度的一个重要考虑事项是,与这些块支持的功能数量相比,细粒度实现需要进入和退出每个块的连接数量相对较大。当块的粒度增加到中粒度或更高时,与它们能够支持的功能相比,进入块的连接数量会减少。这是很重要的一个权衡点,因为当信号通过FPGA传播时,可编程的块间互连处理了绝大多数与信号相关的延迟任务。

这两个架构各有优缺点。细粒度FPGA的逻辑功能块一般较小,仅由很小的几个晶体管组成,非常类似于半定制门阵列的基本单元,其优点是功能块的资源可以被完全利用,缺点是完成复杂的逻辑功能需要大量的连线和开关,因而速度慢;粗粒度FPGA的逻辑块规模大,功能强,完成复杂逻辑只需较少的功能块和内部连线,因而能获得较好的性能,缺点是功能块的资源有时不能被充分利用。

逻辑块(Logic Blocks)

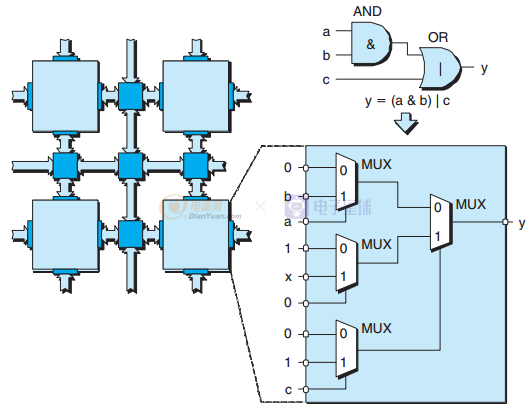

可编程逻辑块有两种基本形式:基于MUX(多路复用器)和基于LUT(查找表)。

基于MUX。作为基于mux的方法的一个例子,考虑一种方法3输入函数y (a & b) |c可以用一个只包含多路复用器的块来实现。

可以对设备进行编程,使对该块的每个输入都用逻辑0、逻辑1或来自另一个块或设备主输入的信号(a、b或c)的1或0表示。这允许以无数种方式配置每个块,以实现大量可能的功能。

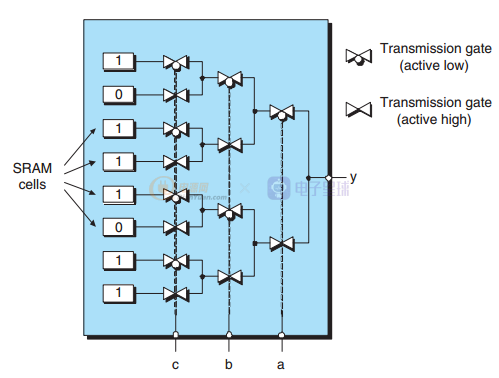

基于LUT。LUT背后的基本概念相对简单。一组输入信号用作查找表的索引(指针)。该表的内容被安排为每个输入组合指向的单元格包含所需的值。例如,我们假设我们希望实现这个函数:

y=(a&b)|c

这可以通过加载一个具有适当值的3输入LUT来实现。为了下面的例子的目的,我们假设LUT是由SRAM单元形成的(也可以使用反熔丝、E2PROM或Flash单元形成)。一种常用的技术是使用如图所示的级联传输门来选择所需的SRAM单元。以配置的目的将它们连接在一起——也就是说,用所需的值加载它们。

如果传输门被激活,它将在输入端看到的信号传递到输出端。如果栅极被禁用,它的输出与它驱动的电线是电断开的。传输门的符号显示一个小圆圈,表明这些门将被一个逻辑0在他们的控制输入激活。相比之下,没有圆圈的符号表示这些门将被逻辑1激活。基于这种理解,很容易看到如何使用不同的输入组合来选择不同SRAM单元的内容。

这两种架构的产品,都各有各有优势。MUX架构在实现大量独立小微逻辑功能时,大大的增加了硅利用率,以及编程效率。LUT则在实现小功能时会占用整个LUT单元,导致浪费。而LUT架构在很多器件中,也能通常被用作小块RAM,提高了灵活性。

后面将会着重继续深入逻辑块方面的介绍。